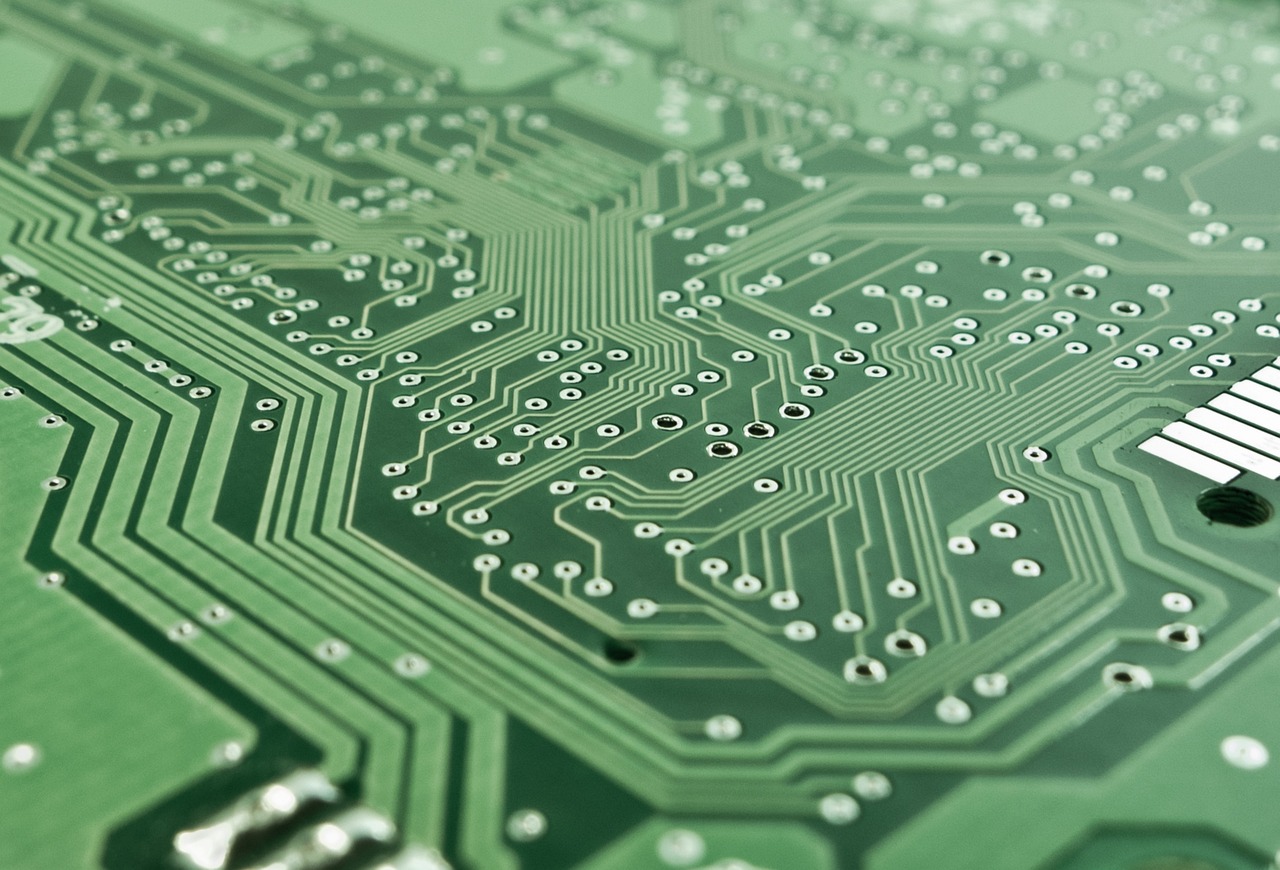

How to Optimize PCB Layout for High-Speed Signals

Understanding High-Speed Design Challenges

As signal speeds increase, traditional PCB design approaches become inadequate. High-speed designs must account for signal integrity issues, crosstalk, and electromagnetic interference.

Impedance Control

Controlled impedance is fundamental to high-speed design. Calculate and maintain consistent trace impedance (typically 50Ω or 100Ω differential) throughout your signal paths.

Length Matching

For differential pairs and parallel buses, length matching ensures signals arrive simultaneously. Use serpentine routing to match trace lengths within specified tolerances.

Layer Stack-up Planning

Proper layer stack-up is critical. Place signal layers adjacent to ground planes for controlled impedance and good return paths.

Differential Pair Routing

Maintain consistent spacing and symmetry when routing differential pairs. Keep pairs tightly coupled and avoid splitting them across different layers when possible.

Via Management

Minimize vias in high-speed signal paths as they introduce impedance discontinuities. When vias are necessary, use appropriate back-drilling techniques.

Power Integrity

Ensure clean power delivery with proper decoupling capacitors, power plane distribution, and low-impedance power delivery networks.

Conclusion

High-speed PCB design requires careful planning and attention to detail. By following these guidelines, you can achieve reliable signal integrity in your designs.

Share this article

Send Your Inquiry Today

We'll respond to your inquiry within 24 hours